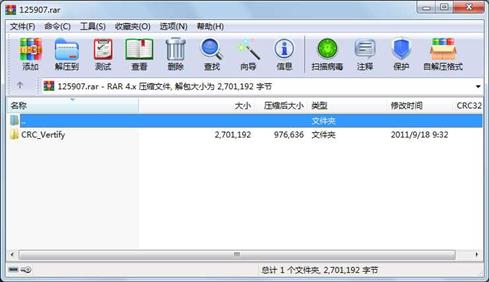

资源简介

CRC32 算法的FPGA实现和C语言实现

代码片段和文件信息

//======================================================== file = crc32.c =====

//= Program to compute CRC-32 using the “table method“ for 8-bit subtracts =

//=============================================================================

//= Notes: Uses the standard “Charles Michael Heard“ code available from =

//= http://cell-relay.indiana.edu/cell-relay/publications/software =

//= /CRC which was adapted from the algorithm described by Avarm =

//= Perez “Byte-wise CRC Calculations“ IEEE Micro 3 40 (1983). =

//=---------------------------------------------------------------------------=

//= Build: bcc32 crc32.c gcc crc32.c =

//=---------------------------------------------------------------------------=

//= History: KJC (8/24/00) - Genesis (from Heard code see above) =

//=============================================================================

//----- Include files ---------------------------------------------------------

#include // Needed for printf()

#include // Needed for rand()

//----- Type defines ----------------------------------------------------------

typedef unsigned char byte; // Byte is a char

typedef unsigned short int word16; // 16-bit word is a short int

typedef unsigned int word32; // 32-bit word is an int

//----- Defines ---------------------------------------------------------------

#define POLYNOMIAL 0x04c11db7L // Standard CRC-32 ppolynomial

// #define BUFFER_LEN 4096L // Length of buffer

#define BUFFER_LEN 8L // Length of buffer

//----- Gloabl variables ------------------------------------------------------

static word32 crc_table[256]; // Table of 8-bit remainders

//----- Prototypes ------------------------------------------------------------

void gen_crc_table(void);

word32 update_crc(word32 crc_accum byte *data_blk_ptr word32 data_blk_size);

//===== Main program ==========================================================

void main(void)

{

byte buff[BUFFER_LEN]; // Buffer of packet bytes

word32 crc32; // 32-bit CRC value

word16 i; // Loop counter (16 bit)

word32 j; // Loop counter (32 bit)

// Initialize the CRC table

gen_crc_table();

// Load buffer with BUFFER_LEN random bytes

// for (i=0; i

buff[0] = 0x01;

buff[1] = 0x23;

buff[2] = 0x45;

buff[3] = 0x67;

buff[4] = 0x89;

buff[5] = 0xAB;

buff[6] = 0xCD;

buff[7] = 0xEF;

// Compute and output CRC

crc32 = update_crc(-1 buff BUFFER_LEN);

printf(“CRC = %08X \n“ crc32);

}

//=============================================================================

//= CRC32 table initialization =

//================================================================= 属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 3933 2011-09-16 15:13 CRC_Vertify\C Demo\Demo1\crc32.c

文件 4145 2011-09-16 15:13 CRC_Vertify\C Demo\Demo1\Debug\crc32.obj

文件 172119 2011-09-16 15:14 CRC_Vertify\C Demo\Demo1\Debug\Demo1.exe

文件 180092 2011-09-16 15:14 CRC_Vertify\C Demo\Demo1\Debug\Demo1.ilk

文件 184772 2011-09-06 16:39 CRC_Vertify\C Demo\Demo1\Debug\Demo1.pch

文件 427008 2011-09-16 15:14 CRC_Vertify\C Demo\Demo1\Debug\Demo1.pdb

文件 33792 2011-09-16 16:04 CRC_Vertify\C Demo\Demo1\Debug\vc60.idb

文件 45056 2011-09-16 15:13 CRC_Vertify\C Demo\Demo1\Debug\vc60.pdb

文件 4270 2011-09-06 21:18 CRC_Vertify\C Demo\Demo1\Demo1.dsp

文件 518 2011-09-06 16:38 CRC_Vertify\C Demo\Demo1\Demo1.dsw

文件 41984 2011-09-18 09:34 CRC_Vertify\C Demo\Demo1\Demo1.ncb

文件 53760 2011-09-18 09:34 CRC_Vertify\C Demo\Demo1\Demo1.opt

文件 244 2011-09-16 16:04 CRC_Vertify\C Demo\Demo1\Demo1.plg

文件 1008640 2011-09-18 09:32 CRC_Vertify\CRC程序使用说明.vsd

文件 8381 2011-09-02 10:24 CRC_Vertify\FPGA_verilog\CRC32_D32_AAL5.v

文件 1587 2011-09-18 09:36 CRC_Vertify\FPGA_verilog\CRC32_D32_AAL5_tb.v

文件 3313 2011-09-02 10:24 CRC_Vertify\FPGA_verilog\CRC32_D8_AAL5.v

文件 1693 2011-09-18 09:37 CRC_Vertify\FPGA_verilog\CRC32_D8_AAL5_tb.v

文件 1381 2011-09-18 09:32 CRC_Vertify\FPGA_verilog\test.cr.mti

文件 75772 2011-09-18 09:32 CRC_Vertify\FPGA_verilog\test.mpf

文件 451 2011-09-06 14:32 CRC_Vertify\FPGA_verilog\Test_CRC_01.m

文件 391 2011-09-06 13:44 CRC_Vertify\FPGA_verilog\transc

文件 65536 2011-09-18 09:32 CRC_Vertify\FPGA_verilog\vsim.wlf

文件 187048 2011-09-18 09:12 CRC_Vertify\FPGA_verilog\work\@c@r@c32_@d32_@a@a@l5\verilog.asm

文件 9237 2011-09-18 09:12 CRC_Vertify\FPGA_verilog\work\@c@r@c32_@d32_@a@a@l5\verilog.rw

文件 14758 2011-09-16 15:08 CRC_Vertify\FPGA_verilog\work\@c@r@c32_@d32_@a@a@l5\_primary.dat

文件 48616 2011-09-16 15:08 CRC_Vertify\FPGA_verilog\work\@c@r@c32_@d32_@a@a@l5\_primary.dbs

文件 422 2011-09-18 09:12 CRC_Vertify\FPGA_verilog\work\@c@r@c32_@d32_@a@a@l5\_primary.vhd

文件 9800 2011-09-18 09:12 CRC_Vertify\FPGA_verilog\work\@c@r@c32_@d32_@a@a@l5_tb\verilog.asm

文件 2684 2011-09-18 09:12 CRC_Vertify\FPGA_verilog\work\@c@r@c32_@d32_@a@a@l5_tb\verilog.rw

............此处省略29个文件信息

相关资源

- VC++ 多线程文件读写操作

- 移木块游戏,可以自编自玩,vc6.0编写

- MFC数字钟(基于VC6.0)

- 安科瑞智能电能表MODBUS通讯程序 VC6

- VC++MFC小游戏实例教程(实例)+MFC类库

- VC6LineNumberAddin.dll

- 用VC6.0实现多边形扫描线填充算法

- VC++实现CMD命令执行与获得返回信息

- VC助手 VC6.0助手

- crc16/32计算(crc16_32.c)

- VC++基于OpenGL模拟的一个3维空间模型

- 基于VC++的SolidWorks二次开发SolidWorks

- VC6 USB开发源码

- VC操作SQLSERVER数据库

- aes加解密(vc源程序)

- vc_串口通讯

- 吕鑫vc6c++数据结构视频源码

- 派克变换VC++源码(附文档)

- 基于opencv漫水填充算法综合

- VC++ 串口

- VC++ 大富翁4_大富翁游戏源码

- MFC的异步网络通讯应用程序

- VC++ 摄像头视频采集与回放源程序

- 转 VC++ 实现电子邮件(Email)发送

- 基于MFC的VC++仿QQ浏览器源码(雏形)

- VC++ 服务程序编写及安装与卸载

- VC++6.0番茄西红柿VAXvirsual assist X完美破

- VC编程助手2010破解版(原名VA_X_10.6.

- 基于改进的fcm算法的图像分割vc++

- VC++6.0 绿色版,免安装,非常好用。

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论