资源简介

基于MIPS指令集的32位五级流水线的CPU设计与Verilog实现。该CPU可以实现28条基本指令。基于SMIC 0.25μm工艺库,使用Design Compile与NC Verilog对设计分别进行逻辑综合和后仿,根据面积、时序等信息对设计进行了优化。最后,为该CPU添加了共享总线,以及UART与GPIO接口,实现了一个简单的SoC,并编写了测试代码,在Modelsim上完成了功能仿真和时序仿真。

代码片段和文件信息

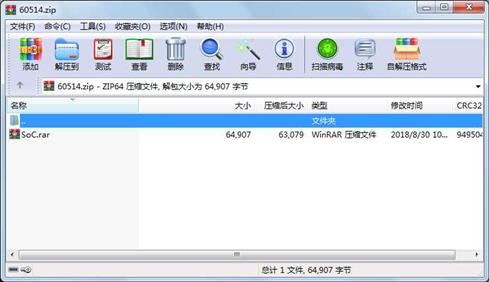

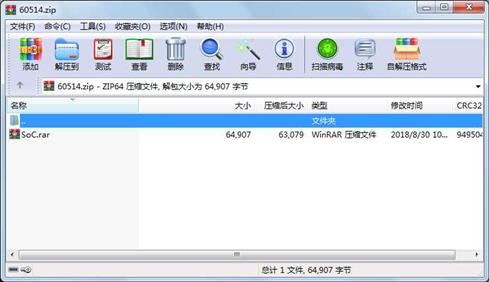

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 64907 2018-08-30 10:02 SoC.rar

----------- --------- ---------- ----- ----

文件 64907 2018-08-30 10:02 SoC.rar

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论