资源简介

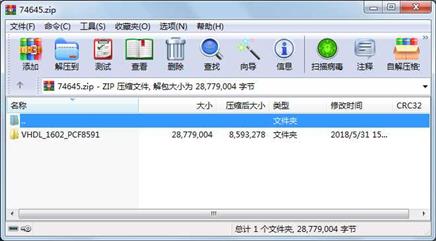

VHDL驱动PCF8591完成4通道电压的采集,并将结果发送的LCD1602进行显示。工程采用QII13.0创建,芯片为ALTERA EP2C8T144C8TN。

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

目录 0 2018-05-31 15:20 VHDL_1602_PCF8591\

文件 2293 2016-12-02 20:06 VHDL_1602_PCF8591\Baud_Rate.bsf

文件 1773 2016-12-02 20:08 VHDL_1602_PCF8591\Baud_Rate.vhd

文件 1773 2016-12-02 20:06 VHDL_1602_PCF8591\Baud_Rate.vhd.bak

文件 2379 2017-06-27 19:37 VHDL_1602_PCF8591\KEY4X4.bsf

文件 2465 2017-06-27 19:50 VHDL_1602_PCF8591\KEY4X4.vhd

文件 7120 2017-06-26 21:35 VHDL_1602_PCF8591\KEY4X4.vhd.bak

文件 4077 2016-12-03 14:45 VHDL_1602_PCF8591\LCD_12864.vhd

文件 15767 2016-11-30 15:47 VHDL_1602_PCF8591\LCD_12864.vhd.bak

文件 4064 2018-05-30 16:13 VHDL_1602_PCF8591\LED_CRL.bsf

文件 8386 2018-05-31 09:41 VHDL_1602_PCF8591\LED_CRL.vhd

文件 5153 2017-06-26 14:25 VHDL_1602_PCF8591\LED_CRL.vhd.bak

文件 8069 2017-06-28 09:29 VHDL_1602_PCF8591\LED_CRL1.vhd

文件 7263 2017-06-27 21:11 VHDL_1602_PCF8591\LED_CRL1.vhd.bak

文件 5677 2016-12-03 15:31 VHDL_1602_PCF8591\Mif1.mif

文件 2782 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.bsf

文件 903 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.cmp

文件 351 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.ppf

文件 431 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.qip

文件 14925 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.vhd

文件 120 2016-12-04 10:33 VHDL_1602_PCF8591\PLLJ_PLLSPE_INFO.txt

文件 2351 2016-12-03 08:36 VHDL_1602_PCF8591\PS2_KEY.bsf

文件 3678 2016-12-03 15:33 VHDL_1602_PCF8591\PS2_KEY.vhd

文件 429 2016-12-03 08:11 VHDL_1602_PCF8591\PS2_KEY.vhd.bak

文件 3067 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.bsf

文件 970 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.cmp

文件 357 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.qip

文件 6291 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.vhd

文件 7994 2018-05-31 09:41 VHDL_1602_PCF8591\TEST.asm.rpt

文件 29590 2018-05-31 09:07 VHDL_1602_PCF8591\TEST.bdf

文件 333 2018-05-31 09:41 VHDL_1602_PCF8591\TEST.cdf

............此处省略1809个文件信息

----------- --------- ---------- ----- ----

目录 0 2018-05-31 15:20 VHDL_1602_PCF8591\

文件 2293 2016-12-02 20:06 VHDL_1602_PCF8591\Baud_Rate.bsf

文件 1773 2016-12-02 20:08 VHDL_1602_PCF8591\Baud_Rate.vhd

文件 1773 2016-12-02 20:06 VHDL_1602_PCF8591\Baud_Rate.vhd.bak

文件 2379 2017-06-27 19:37 VHDL_1602_PCF8591\KEY4X4.bsf

文件 2465 2017-06-27 19:50 VHDL_1602_PCF8591\KEY4X4.vhd

文件 7120 2017-06-26 21:35 VHDL_1602_PCF8591\KEY4X4.vhd.bak

文件 4077 2016-12-03 14:45 VHDL_1602_PCF8591\LCD_12864.vhd

文件 15767 2016-11-30 15:47 VHDL_1602_PCF8591\LCD_12864.vhd.bak

文件 4064 2018-05-30 16:13 VHDL_1602_PCF8591\LED_CRL.bsf

文件 8386 2018-05-31 09:41 VHDL_1602_PCF8591\LED_CRL.vhd

文件 5153 2017-06-26 14:25 VHDL_1602_PCF8591\LED_CRL.vhd.bak

文件 8069 2017-06-28 09:29 VHDL_1602_PCF8591\LED_CRL1.vhd

文件 7263 2017-06-27 21:11 VHDL_1602_PCF8591\LED_CRL1.vhd.bak

文件 5677 2016-12-03 15:31 VHDL_1602_PCF8591\Mif1.mif

文件 2782 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.bsf

文件 903 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.cmp

文件 351 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.ppf

文件 431 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.qip

文件 14925 2018-05-28 09:37 VHDL_1602_PCF8591\PLL.vhd

文件 120 2016-12-04 10:33 VHDL_1602_PCF8591\PLLJ_PLLSPE_INFO.txt

文件 2351 2016-12-03 08:36 VHDL_1602_PCF8591\PS2_KEY.bsf

文件 3678 2016-12-03 15:33 VHDL_1602_PCF8591\PS2_KEY.vhd

文件 429 2016-12-03 08:11 VHDL_1602_PCF8591\PS2_KEY.vhd.bak

文件 3067 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.bsf

文件 970 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.cmp

文件 357 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.qip

文件 6291 2016-12-03 15:31 VHDL_1602_PCF8591\ROM1.vhd

文件 7994 2018-05-31 09:41 VHDL_1602_PCF8591\TEST.asm.rpt

文件 29590 2018-05-31 09:07 VHDL_1602_PCF8591\TEST.bdf

文件 333 2018-05-31 09:41 VHDL_1602_PCF8591\TEST.cdf

............此处省略1809个文件信息

相关资源

- FPGA实现PID.v

- 基于FPGA的sdi视频传输工程(k7_sdi_rx

- FPGA彩条显示

- Xilinx-FPGA-引脚功能详细介绍.doc

- 基于xilinx FPGA的PCIe设计实战

- 基于PCIe的FPGA动态配置设计与实现

- 为什么工程师要掌握FPGA开发知识?

- 八三编码器设计 VHDL代码 简单,包附

- 数字频率合成dds正弦波基于FPGA的DDS产

- 3人表决器 QuartusII

- Verilog FPGA UART串口控制器

- 六路智能抢答器VHDL语言

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- FPGA在步进电机驱动上的应用实例及代

- vhdl与lcd1602实现的多控制电子钟

- verilog的PCI源代码,非常详细,顶层模

- fpga实现频率测量

- FPGA开发-ChipScope教程

- ASK调制与解调VHDL程序及仿真

- 红外循迹小车VHDL程序

- VHDL学习及实例(100个例子)

- VHDL 7人表决器

- VHDL语言编写的100实用的例程

- VHDL写的四人抢答器

- lcd12864的VHDL程序

- 基于VHDL的交通灯控制器设计

- VHDL带分频功能的函数发生器实现六种

- 基于FPGA的USB接口设计

- DE2模拟的交通红绿灯

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论