-

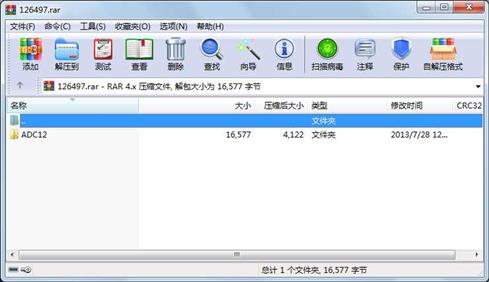

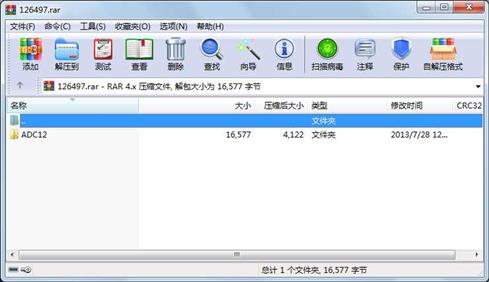

大小: 4KB文件类型: .rar金币: 2下载: 0 次发布日期: 2021-05-28

- 语言: 其他

- 标签: MSP430 MSP430F5529 ADC12

资源简介

MSP430F5529 ADC12模块程序,包含单通道多次采样和多通道多次采样

代码片段和文件信息

/***********************************************************************

*

* 设备 : MSP430f5529

* 名称 : ADC采样

* 功能 : ADC12模块程序

*

* 2013/7/28

* Sunchy

*

***********************************************************************/

#include “ADC12.h“

/********************单通道多次采样**********************/

void ADC12_SET_SINGLE_REPEATED(uchar inch){

//----------------ADC12CTL0

// ADC12SHT1x & ADC12SHT0x ADC12_A sample-and-hold time

// 1x : ADC12MEM8 to ADC12MEM15 0x : ADC12MEM0 to ADC12MEM7

// 0000b:4 ADC12CLK cycles 0001b:8 0100b:64

// ADC12MSC ADC12_A multiple sample and conversion. valid only for sequence or repeated modes

// ADC12REF2_5V reference generator voltage 0b:1.5V 1b:2.5V

// ADC12REFON reference generator on 0b:reference off 1b:on

// ADC12ON 1b:ADC12_A on

// ADC12OVIE ADC12MEMx overflow-interrupt enable

// ADC12TOVIE ADC12_A conversion-time-overflow interrupt enable

// ADC12ENC ADC12_A enable conversion 1b:enable

// ADC12SC ADC12_A start conversion 1b:start reset automatically

//---------------ADC12CTL0 END

ADC12CTL0 = ADC12ON+ADC12SHT0_8+ADC12MSC; // Turn on ADC12set sample-and-hold time 64*ADC12CLK

// set multiple sample conversion

//---------------ADC12CTL1

// ADC12CSTARTADDx ADC12_A conversion start address

// for single conversion or for the first conversion in a sequence

// ADC12SHSx ADC12_A sample-and-hold source select

// 00b:ADC12SC bit 01b:Timer_A 0.1 10b:Timer_B 0.0 11b:Timer_B 0.1

// ADC12SHP sample-and-hold pulse-mode select

// ADC12ISSH invert signal sample-and-hold 1b:inverted

// ADC12DIVx clock divider

// 000b:divide by 1 001b: 2 111b: 8

// ADC12SSELx clock source select

// 00b:ADC12OSC(MODOSC) 01b:ACLK 10b:MCLK 11b:SMCLK

// ADC12CONSEQx conversion sequence mode select

// 00b:Single-channelsingle-conversion 01b:Sequence-of-channels

// 01b:Repeated-single-channel 11b:Repeated-sequence-of-channels

// ADC12BUSY ADC12_A busy 1b:A sequencesample or conversion is active

//--------------ADC12CTL1 END

ADC12CTL1 = ADC12SHP+ADC12CONSEQ_2; // Select sample-and-hold pulse-mode

// Repeated-single-channel

ADC12CTL1 &= ~(ADC12CSTARTADD3+\

ADC12CSTARTADD2+\

ADC12CSTARTADD1+\

ADC12CSTARTADD0); // conversion start address

//--------------ADC12CTL2

// ADC12PDIV ADC12_A predivider 0b:predivider by 1 1b:predivider by 4

// ADC12TCOFF temperature sensor off

// ADC12RES ADC12_A conversion result resolution

// 00b:8 bit 01b:10 bit 10b:12bit

// ADC12DF data read-back format. Data is always stored in the binary unsigned format.

// 0b:binary unsigned. -VREF : 0000h +VREF : 0fffh

// 1b:signed binaryleft aligned. -VREF : 8000h +VREF : 7FF0h

// ADC12SR sampling rate 0b:approximately 200 ksps 1b:50 ksps

// ADC12REFOUT reference output 1b:reference output on

// ADC12REFBURST reference burst

//----------属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 11127 2013-07-28 12:34 ADC12\ADC12.c

文件 1855 2013-07-28 12:35 ADC12\ADC12.h

文件 3395 2013-07-28 12:30 ADC12\main.c

文件 200 2013-07-28 12:42 ADC12\read me.txt

目录 0 2013-07-28 12:36 ADC12

----------- --------- ---------- ----- ----

16577 5

- 上一篇:关于QT多线程子线程使用信号和槽

- 下一篇:正版熊族.EXE

相关资源

- IAR for MSP430 v7.10.1 注册机

- 基于MSP430G2553的蓝牙控制小车

- 利用DS1302和msp430进行闹钟和万年历的

- msp430F149操作红外接收模块源码

- [免费]msp430f149控制PS2键盘并用1602显示

- MSP430f149读sd FAT txt

- 用8位spi实现16位spi

- 基于MSP430单片机的实时多任务操作系

- 超声处理原位反应合成Al2O3/ADC12复合材

- MSP430系列单片机例程(msp430f235)

- MSP430控制AD9850产生频率可调的方波及

- msp430f449程序

- 基于MSP430的数控直流电压源

- MSP430F5438A Timer_B 操作实验

- MSP430F5438 UCS 时钟操作实验

- MSP430F5438A Timer_A 操作实验

- MSP430F5438 看门狗实验

- IAR EW430连接仿真器在线仿真

- 初识畅学系列MSP430F149单片机开发板

- 畅学多功能实验箱 MSP430F5438 RTC 操作实

- MSP430F5438A RAM操作实验

- msp430f5438a技术资料

- MSP430 JTAGUSB的和并口的与目标板连接的

- MSP430教程:MSP430单片机ADC12模块

- WIA-PA网络技术在井下人员定位系统中

- 16位MSP430单片机的开关稳压电源设计

- 基于mps430f149的12864液晶显示模块编程

- MSP430F5529移植modbus

- MSP430详细教程

- MSP430信号发生器.rar

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论