资源简介

用锁相环实现的频率合成器既有频率稳定度高又有改换频率方便的优点。实现输出频率N倍于输入频率(fo=N•fi),且在一定频率范围内其输出信号的稳定度完全跟踪输入信号。因而在现代通信和嵌入式系统中获得广泛应用。

电源+5V;集成电路芯片4046、74LS191(各一片);输入信号由信号发生器提供;输入信号频率范围10HZ~1kHZ;

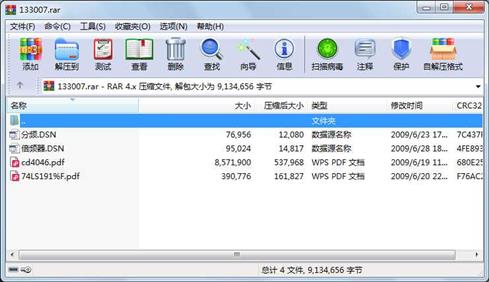

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 95024 2009-06-28 18:22 倍频器.DSN

文件 76956 2009-06-23 17:17 分频.DSN

文件 390776 2009-06-20 22:29 74LS191%F.pdf

文件 8571900 2009-06-19 11:20 cd4046.pdf

----------- --------- ---------- ----- ----

9134656 4

----------- --------- ---------- ----- ----

文件 95024 2009-06-28 18:22 倍频器.DSN

文件 76956 2009-06-23 17:17 分频.DSN

文件 390776 2009-06-20 22:29 74LS191%F.pdf

文件 8571900 2009-06-19 11:20 cd4046.pdf

----------- --------- ---------- ----- ----

9134656 4

- 上一篇:基于51单片机的8路AD电压采集与测量

- 下一篇:FOR循环语句的翻译程序设计

相关资源

- 数字正交上变频器AD9857在高频雷达系

- 利用高压VCO设计高性能锁相环

- 翻译的美国大学经典参考书,Roland

- 锁相环回路滤波器设计优化

- PLL原理讲义 一个典型的锁相环PLL系统

- 改善分数分频锁相环合成器中的整数

- 锁相环PLL偏离整数通道的频率点杂散

- 宽频带数字锁相环的设计及基于FPGA的

- PLL和DLL:都是锁相环,区别在哪里?

- 基于锁相环的低频函数发生器

- 一种基于FPGA的三相锁相环设计方法

- 一种无锁相环i_p-i_q检测新方法

- 锁相环技术原理及FPGA实现

- QPSK与BPSK的锁相环仿真源码

- 锁相环设计、模拟、应用第5版 ,,很

- 锁相技术 张厥盛 数字锁相环

- 锁相环程序代码

- 二阶锁频辅助三阶锁相环路滤波器设

- 锁相环频率合成器 pdf版

- 基于STM32F4系列的4个编码器4倍频的转

- 基于CD4046锁相环的频率合成计

- 锁相环频率合成器.pdf

- 用于锁相环的两级ring VCO设计

- 锁相环pll工作原理及verilog代码

- quartusii的PLL IP核分频和倍频

- 通信中的同步技术及应用 - 季仲梅(

- ADI的锁相环PLL仿真工具ADIsimPLL3.4.06及

- 自己整理的锁相环的ads仿真,找了很

- 锁相环PLL基本原理.pdf

- 基于FPGA的数字锁相环设计

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论