资源简介

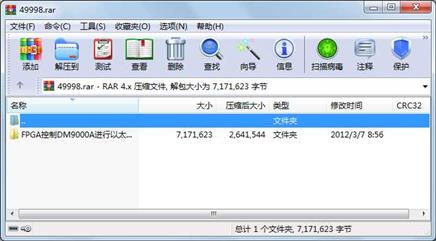

FPGA 控制DM9000A进行以太网数据收发的Verilog实现

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 3028 2007-10-18 15:47 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a.def

文件 39376 2007-10-18 15:26 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_Init.v

文件 2319 2007-10-17 18:54 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_IO.v

文件 5696 2007-10-18 14:35 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_Ior.v

文件 3168 2007-10-17 19:07 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_IORD.v

文件 4287 2007-10-17 19:34 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_Iow.v

文件 3253 2007-10-17 19:15 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_IOWR.v

文件 10332 2007-10-17 19:41 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\phy_write.v

文件 160 2007-11-20 10:53 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\vssver.scc

文件 9426 2007-07-31 20:49 FPGA控制DM9000A进行以太网数据收发的Verilog实现\DM9000A.C

文件 3722 2007-09-15 14:15 FPGA控制DM9000A进行以太网数据收发的Verilog实现\DM9000A.H

文件 1765212 2006-03-14 15:31 FPGA控制DM9000A进行以太网数据收发的Verilog实现\DM9000A.pdf

文件 1484824 2007-12-19 02:46 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a和FPGA的接口全图.jpg

文件 441685 2008-03-09 16:57 FPGA控制DM9000A进行以太网数据收发的Verilog实现\FPGA控制DM9000A进行以太网数据收发的Verilog实现 - 恋恋风尘.mht

文件 136 2008-03-09 16:29 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\db\Dm9000a_Init.db_info

文件 8572 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.asm.rpt

文件 26 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.done

文件 129181 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.fit.rpt

文件 513 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.fit.smsg

文件 618 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.fit.summary

文件 5633 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.flow.rpt

文件 26487 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.map.rpt

文件 93 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.map.smsg

文件 475 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.map.summary

文件 31228 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.pin

文件 2097339 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.pof

文件 915 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.qpf

文件 4622 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.qsf

文件 587 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.qws

文件 475714 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.sof

............此处省略56个文件信息

----------- --------- ---------- ----- ----

文件 3028 2007-10-18 15:47 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a.def

文件 39376 2007-10-18 15:26 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_Init.v

文件 2319 2007-10-17 18:54 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_IO.v

文件 5696 2007-10-18 14:35 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_Ior.v

文件 3168 2007-10-17 19:07 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_IORD.v

文件 4287 2007-10-17 19:34 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_Iow.v

文件 3253 2007-10-17 19:15 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\Dm9000a_IOWR.v

文件 10332 2007-10-17 19:41 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\phy_write.v

文件 160 2007-11-20 10:53 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a\vssver.scc

文件 9426 2007-07-31 20:49 FPGA控制DM9000A进行以太网数据收发的Verilog实现\DM9000A.C

文件 3722 2007-09-15 14:15 FPGA控制DM9000A进行以太网数据收发的Verilog实现\DM9000A.H

文件 1765212 2006-03-14 15:31 FPGA控制DM9000A进行以太网数据收发的Verilog实现\DM9000A.pdf

文件 1484824 2007-12-19 02:46 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Dm9000a和FPGA的接口全图.jpg

文件 441685 2008-03-09 16:57 FPGA控制DM9000A进行以太网数据收发的Verilog实现\FPGA控制DM9000A进行以太网数据收发的Verilog实现 - 恋恋风尘.mht

文件 136 2008-03-09 16:29 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\db\Dm9000a_Init.db_info

文件 8572 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.asm.rpt

文件 26 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.done

文件 129181 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.fit.rpt

文件 513 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.fit.smsg

文件 618 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.fit.summary

文件 5633 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.flow.rpt

文件 26487 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.map.rpt

文件 93 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.map.smsg

文件 475 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.map.summary

文件 31228 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.pin

文件 2097339 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.pof

文件 915 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.qpf

文件 4622 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.qsf

文件 587 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.qws

文件 475714 2007-12-19 03:02 FPGA控制DM9000A进行以太网数据收发的Verilog实现\Test\Dm9000a_Init\Dm9000a_Init.sof

............此处省略56个文件信息

- 上一篇:深度学习在量化投资中的应用

- 下一篇:TrueRTA 3.5.5 +注册机 破解版

相关资源

- FPGA实现PID.v

- 基于FPGA的sdi视频传输工程(k7_sdi_rx

- FPGA彩条显示

- Xilinx-FPGA-引脚功能详细介绍.doc

- 基于xilinx FPGA的PCIe设计实战

- 基于PCIe的FPGA动态配置设计与实现

- 为什么工程师要掌握FPGA开发知识?

- Quartus II 15.0中仿真Altera三速以太网I

- Quartus II 15.0中仿真Altera三速以太网I

- 数字频率合成dds正弦波基于FPGA的DDS产

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- FPGA在步进电机驱动上的应用实例及代

- fpga实现频率测量

- 基于DSP2812的以太网调试程序

- FPGA开发-ChipScope教程

- 红外循迹小车VHDL程序

- 基于FPGA的USB接口设计

- DE2模拟的交通红绿灯

- 一种抗SEU存储器电路的FPGA设计

- Cyclone 10LP Remote Update Intel FPGA IP 官方工

- Intel 82579LM 82579V千兆以太网控制器驱动

- nRF24L01无线模块在单片机与FPGA上的应

- 基于FPGA多协议转换网关设计

- 万兆以太网技术特点及应用

- 光以太网技术及在城域光网络的应用

- 光以太网技术在IP城域光网络中的应用

- 电信级以太网技术漫谈

- 基于VGA的Flappy Bird的Verilog实现(源码

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论