资源简介

数字混频的Veriloag代码,Quartus工程,含testbench仿真。程序设计系统时钟5MHz,625kHz的输入信号与625kHz的本振信号做混频,根据混频原理会得到1.25MHz的和频信号与0Hz(直流),将直流滤除掉得到1.25MHz的有效信号。

代码片段和文件信息

% Altera NCO version 9.0

% function [sc] = oc_model(phi_inc_iphase_mod_ifreq_mod_i)

% input : phi_inc_i : phase increment input (required)

% phase_mod_i : phase modulation input(optional)

% freq_mod_i : frequency modulation input(optional)

% output : s : sine wave output

% c : cosine wave output

function [sc] = oc_model(phi_inc_iphase_mod_ifreq_mod_i)

addpath c:/altera/12.1/ip/altera/nco/lib/ip_toolbench/../;

if(nargin==0)

fprintf(‘Error using oc_model : Not enough input arguments\n‘);

else

N=length(phi_inc_i);

end

if(nargin==1)

phase_mod_i=zeros(1N);

freq_mod_i=zeros(1N);

elseif(nargin==2)

if(length(phase_mod_i)~=N)

fprintf(‘Error using oc_model : input vector length mismatch\n‘);

else

freq_mod_i=zeros(1N);

end

elseif(nargin==3)

if((length(phase_mod_i)~=N)|length(freq_mod_i)~=N)

fprintf(‘Error using oc_model : input vector length mismatch\n‘);

end

else

fprintf(‘Error using oc_model : Incorrect number of input arguments\n‘);

end

N=length(phi_inc_i);

numch = 1.0;

apr = 16.0;

apri = 16.0;

mpr = 10.0;

aprp = 16.0;

aprf = 32.0;

dpri = 5.0;

arch = 0.0;

wantFmod = 0.0;

wantPmod = 0.0;

dual = 1.0;

[sc] = Sncomodel(phi_inc_iphase_mod_ifreq_mod_iwantFmodwantPmodnumchaprmprapriaprpaprfdpriarchdualN);

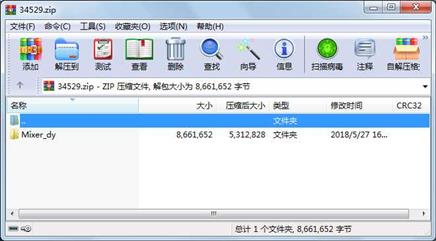

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

目录 0 2018-05-27 16:34 Mixer_dy\

目录 0 2018-05-27 16:34 Mixer_dy\db\

文件 1771 2018-05-27 14:45 Mixer_dy\db\add_sub_15i.tdf

文件 1769 2018-05-27 14:45 Mixer_dy\db\add_sub_qth.tdf

文件 10322 2018-05-27 14:45 Mixer_dy\db\altsyncram_mo81.tdf

文件 10322 2018-05-27 14:45 Mixer_dy\db\altsyncram_ro81.tdf

文件 3202 2018-05-27 14:45 Mixer_dy\db\cntr_ori.tdf

文件 0 2018-05-27 16:29 Mixer_dy\db\logic_util_heursitic.dat

文件 7268 2018-05-27 16:29 Mixer_dy\db\Mixer.(0).cnf.cdb

文件 2360 2018-05-27 16:29 Mixer_dy\db\Mixer.(0).cnf.hdb

文件 1392 2018-05-27 14:45 Mixer_dy\db\Mixer.(1).cnf.cdb

文件 904 2018-05-27 14:45 Mixer_dy\db\Mixer.(1).cnf.hdb

文件 1674 2018-05-27 14:45 Mixer_dy\db\Mixer.(10).cnf.cdb

文件 616 2018-05-27 14:45 Mixer_dy\db\Mixer.(10).cnf.hdb

文件 2494 2018-05-27 14:45 Mixer_dy\db\Mixer.(11).cnf.cdb

文件 823 2018-05-27 14:45 Mixer_dy\db\Mixer.(11).cnf.hdb

文件 869 2018-05-27 14:45 Mixer_dy\db\Mixer.(12).cnf.cdb

文件 770 2018-05-27 14:45 Mixer_dy\db\Mixer.(12).cnf.hdb

文件 2476 2018-05-27 14:45 Mixer_dy\db\Mixer.(13).cnf.cdb

文件 974 2018-05-27 14:45 Mixer_dy\db\Mixer.(13).cnf.hdb

文件 5730 2018-05-27 14:45 Mixer_dy\db\Mixer.(14).cnf.cdb

文件 1790 2018-05-27 14:45 Mixer_dy\db\Mixer.(14).cnf.hdb

文件 1574 2018-05-27 14:45 Mixer_dy\db\Mixer.(15).cnf.cdb

文件 969 2018-05-27 14:45 Mixer_dy\db\Mixer.(15).cnf.hdb

文件 1448 2018-05-27 14:45 Mixer_dy\db\Mixer.(16).cnf.cdb

文件 785 2018-05-27 14:45 Mixer_dy\db\Mixer.(16).cnf.hdb

文件 3591 2018-05-27 14:45 Mixer_dy\db\Mixer.(17).cnf.cdb

文件 714 2018-05-27 14:45 Mixer_dy\db\Mixer.(17).cnf.hdb

文件 1585 2018-05-27 14:45 Mixer_dy\db\Mixer.(18).cnf.cdb

文件 969 2018-05-27 14:45 Mixer_dy\db\Mixer.(18).cnf.hdb

文件 1448 2018-05-27 14:45 Mixer_dy\db\Mixer.(19).cnf.cdb

............此处省略363个文件信息

相关资源

- Xilinx-FPGA-引脚功能详细介绍.doc

- 基于xilinx FPGA的PCIe设计实战

- 基于PCIe的FPGA动态配置设计与实现

- 为什么工程师要掌握FPGA开发知识?

- Quartus II 15.0中仿真Altera三速以太网I

- Quartus II 15.0中仿真Altera三速以太网I

- 数字频率合成dds正弦波基于FPGA的DDS产

- 3人表决器 QuartusII

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- FPGA在步进电机驱动上的应用实例及代

- 硬件课程设计—流水灯(quartus软件

- 曼彻斯特编解码_同步QuartusII工程

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- fpga实现频率测量

- FPGA开发-ChipScope教程

- 红外循迹小车VHDL程序

- CPLD Verilog数字密码锁 源码

- 用quartus 2编的全加器(原理图输入)

- verilog 实现任意分频方法

- 基于FPGA的USB接口设计

- DE2模拟的交通红绿灯

- 6相12拍步进电机控制器

- SPI Master 的Verilog源代码

- 一种抗SEU存储器电路的FPGA设计

- Cyclone 10LP Remote Update Intel FPGA IP 官方工

- nRF24L01无线模块在单片机与FPGA上的应

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论