资源简介

在Verilog语言下用FPGA驱动DS18B20,带数码管显示,带LED报警,有报警值调整功能。这个是本人调过的,原版调通代码没改的,绝对能跑通。建议用QuatusII全编译后看一下RTL图就能理解程序是怎么工作的。

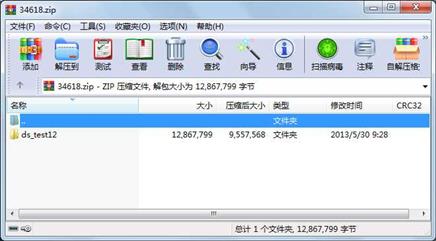

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

目录 0 2013-05-30 09:28 ds_test12\

目录 0 2013-05-30 09:28 ds_test12\.qsys_edit\

文件 69 2013-05-29 15:50 ds_test12\.qsys_edit\filters.xml

文件 494 2013-05-29 15:50 ds_test12\.qsys_edit\preferences.xml

文件 360 2013-05-20 19:07 ds_test12\1_5.v

文件 285 2013-05-20 19:07 ds_test12\1_5.v.bak

文件 303 2013-05-29 08:56 ds_test12\clk_1ms.v

文件 314 2013-05-20 19:07 ds_test12\clk_1ms.v.bak

文件 310 2013-05-20 19:07 ds_test12\clk_1s.v

文件 300 2013-05-20 19:07 ds_test12\clk_1s.v.bak

文件 305 2013-05-27 09:43 ds_test12\clk_1us.v

文件 276 2013-05-27 09:41 ds_test12\clk_1us.v.bak

文件 1515 2013-05-29 16:30 ds_test12\data_cahange.v

文件 141 2013-05-29 11:37 ds_test12\data_cahange.v.bak

目录 0 2013-06-03 18:00 ds_test12\db\

文件 1736 2013-05-29 09:59 ds_test12\db\add_sub_7pc.tdf

文件 1881 2013-05-29 09:59 ds_test12\db\add_sub_8pc.tdf

文件 1435 2013-05-29 09:59 ds_test12\db\add_sub_ngh.tdf

文件 1435 2013-05-29 09:59 ds_test12\db\add_sub_rgh.tdf

文件 39676 2013-05-29 09:59 ds_test12\db\altsyncram_au14.tdf

文件 41824 2013-05-29 10:28 ds_test12\db\altsyncram_eu14.tdf

文件 43972 2013-05-29 10:40 ds_test12\db\altsyncram_iu14.tdf

文件 14738 2013-05-29 09:59 ds_test12\db\alt_u_div_07f.tdf

文件 16928 2013-05-29 09:59 ds_test12\db\alt_u_div_67f.tdf

文件 34688 2013-05-29 09:59 ds_test12\db\alt_u_div_o9f.tdf

文件 1687 2013-05-29 09:59 ds_test12\db\cmpr_ngc.tdf

文件 1919 2013-05-29 09:59 ds_test12\db\cmpr_qgc.tdf

文件 2079 2013-05-29 10:28 ds_test12\db\cmpr_sgc.tdf

文件 3301 2013-05-29 09:59 ds_test12\db\cntr_23j.tdf

文件 3316 2013-05-29 09:59 ds_test12\db\cntr_egi.tdf

文件 3736 2013-05-29 09:59 ds_test12\db\cntr_fgi.tdf

............此处省略348个文件信息

----------- --------- ---------- ----- ----

目录 0 2013-05-30 09:28 ds_test12\

目录 0 2013-05-30 09:28 ds_test12\.qsys_edit\

文件 69 2013-05-29 15:50 ds_test12\.qsys_edit\filters.xm

文件 494 2013-05-29 15:50 ds_test12\.qsys_edit\preferences.xm

文件 360 2013-05-20 19:07 ds_test12\1_5.v

文件 285 2013-05-20 19:07 ds_test12\1_5.v.bak

文件 303 2013-05-29 08:56 ds_test12\clk_1ms.v

文件 314 2013-05-20 19:07 ds_test12\clk_1ms.v.bak

文件 310 2013-05-20 19:07 ds_test12\clk_1s.v

文件 300 2013-05-20 19:07 ds_test12\clk_1s.v.bak

文件 305 2013-05-27 09:43 ds_test12\clk_1us.v

文件 276 2013-05-27 09:41 ds_test12\clk_1us.v.bak

文件 1515 2013-05-29 16:30 ds_test12\data_cahange.v

文件 141 2013-05-29 11:37 ds_test12\data_cahange.v.bak

目录 0 2013-06-03 18:00 ds_test12\db\

文件 1736 2013-05-29 09:59 ds_test12\db\add_sub_7pc.tdf

文件 1881 2013-05-29 09:59 ds_test12\db\add_sub_8pc.tdf

文件 1435 2013-05-29 09:59 ds_test12\db\add_sub_ngh.tdf

文件 1435 2013-05-29 09:59 ds_test12\db\add_sub_rgh.tdf

文件 39676 2013-05-29 09:59 ds_test12\db\altsyncram_au14.tdf

文件 41824 2013-05-29 10:28 ds_test12\db\altsyncram_eu14.tdf

文件 43972 2013-05-29 10:40 ds_test12\db\altsyncram_iu14.tdf

文件 14738 2013-05-29 09:59 ds_test12\db\alt_u_div_07f.tdf

文件 16928 2013-05-29 09:59 ds_test12\db\alt_u_div_67f.tdf

文件 34688 2013-05-29 09:59 ds_test12\db\alt_u_div_o9f.tdf

文件 1687 2013-05-29 09:59 ds_test12\db\cmpr_ngc.tdf

文件 1919 2013-05-29 09:59 ds_test12\db\cmpr_qgc.tdf

文件 2079 2013-05-29 10:28 ds_test12\db\cmpr_sgc.tdf

文件 3301 2013-05-29 09:59 ds_test12\db\cntr_23j.tdf

文件 3316 2013-05-29 09:59 ds_test12\db\cntr_egi.tdf

文件 3736 2013-05-29 09:59 ds_test12\db\cntr_fgi.tdf

............此处省略348个文件信息

相关资源

- Xilinx-FPGA-引脚功能详细介绍.doc

- 基于xilinx FPGA的PCIe设计实战

- 基于PCIe的FPGA动态配置设计与实现

- 为什么工程师要掌握FPGA开发知识?

- 数字频率合成dds正弦波基于FPGA的DDS产

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 单片机与温度传感器DS18B20的程序设计

- 毕业论文之温度传感器DS18B20(源码

- 一个简单的verilog编写的DMA IP CORE,和

- stm32 ds18b20 温度传感器 测试通过

- FPGA在步进电机驱动上的应用实例及代

- 51单片机读取温度数据存储到SD卡中并

- STM32F103 DS18B20 V3.5.0固件库驱动程序工

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- DS18B20分布式多点测温的Proteus仿真

- verilog的PCI源代码,非常详细,顶层模

- 单片机 DS18B20 温度控制系统

- fpga实现频率测量

- 课程设计蔬菜大棚自动控制系统,包

- FPGA开发-ChipScope教程

- 红外循迹小车VHDL程序

- CPLD Verilog数字密码锁 源码

- verilog 实现任意分频方法

- 基于FPGA的USB接口设计

- DE2模拟的交通红绿灯

- SPI Master 的Verilog源代码

- 一种抗SEU存储器电路的FPGA设计

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论