资源简介

本实例是使用verilog HDL语言来进行16位cpu设计。

代码片段和文件信息

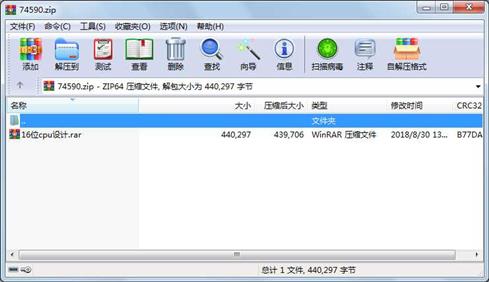

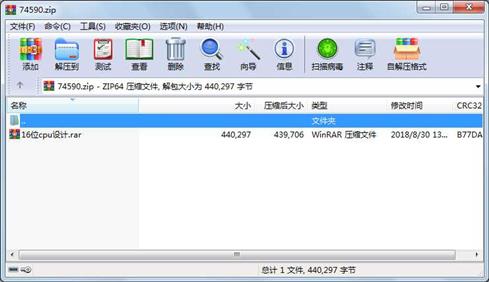

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 440297 2018-08-30 13:34 16位cpu设计.rar

----------- --------- ---------- ----- ----

文件 440297 2018-08-30 13:34 16位cpu设计.rar

- 上一篇:技术研发人员绩效考核方案

- 下一篇:单相PWM整流器PSCAD模型

相关资源

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- CPLD Verilog数字密码锁 源码

- Cpu-Z检测CPU软件

- verilog 实现任意分频方法

- DE2模拟的交通红绿灯

- SPI Master 的Verilog源代码

- 基于VGA的Flappy Bird的Verilog实现(源码

- 数字钟

- Verilog的135个经典设计

- verilog 4×4矩阵键盘

- Quartus EDA交通灯控制电路的设计实训报

- FPGA按键消抖

- 完美获取 CPU 的 NUMA节点数、CPU插槽个

- 用Verilog语言写的CPLD和MCU通讯的SPI接口

- ARM9指令cache的verilog代码

- 高通CPU救砖工具刷入完整资料

- 大话处理器:处理器基础知识读本高

- ddr_verilog

- FPGA实现单极性SPWM调制

- uart_tx.zip

- 移远OpenCPU快速开始指导手册

- ThrottleStop_8.70.6

- 易语言GDI画CPU动态线源码

- 基于Verilog的cordic反正切FPGA例程

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论