-

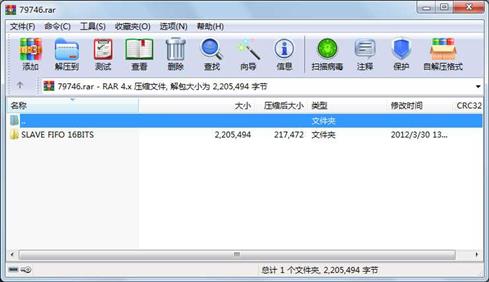

大小: 218KB文件类型: .rar金币: 2下载: 0 次发布日期: 2021-05-17

- 语言: 其他

- 标签: CY7C68013a slavefifo verilog FPGA

资源简介

上传了CY7C68013a的slavefifo的固件源代码,keil编写,以及使用FPGA向EP6端点写数据的verilog源代码,本人亲测,没有错误,可以编译成功,需要的朋友快快下载

代码片段和文件信息

//-----------------------------------------------------------------------------

// File: fw.c

// Contents: Firmware frameworks task dispatcher and device request parser

// source.

//

// indent 3. NO TABS!

//

// $Revision: 17 $

// $Date: 11/15/01 5:45p $

//

// Copyright (c) 1997 AnchorChips Inc. All rights reserved

//-----------------------------------------------------------------------------

#include “fx2.h“

#include “fx2regs.h“

//-----------------------------------------------------------------------------

// Constants

//-----------------------------------------------------------------------------

#define DELAY_COUNT 0x9248*8L // Delay for 8 sec at 24Mhz 4 sec at 48

#define _IFREQ 48000 // IFCLK constant for Synchronization Delay

#define _CFREQ 48000 // CLKOUT constant for Synchronization Delay

//-----------------------------------------------------------------------------

// Random Macros

//-----------------------------------------------------------------------------

#define min(ab) (((a)<(b))?(a):(b))

#define max(ab) (((a)>(b))?(a):(b))

// Registers which require a synchronization delay see section 15.14

// FIFORESET FIFOPINPOLAR

// INPKTEND OUTPKTEND

// EPxBCH:L REVCTL

// GPIFTCB3 GPIFTCB2

// GPIFTCB1 GPIFTCB0

// EPxFIFOPFH:L EPxAUTOINLENH:L

// EPxFIFOCFG EPxGPIFFLGSEL

// PINFLAGSxx EPxFIFOIRQ

// EPxFIFOIE GPIFIRQ

// GPIFIE GPIFADRH:L

// UDMACRCH:L EPxGPIFTRIG

// GPIFTRIG

// Note: The pre-REVE EPxGPIFTCH/L register are affected as well...

// ...these have been replaced by GPIFTC[B3:B0] registers

#include “fx2sdly.h“ // Define _IFREQ and _CFREQ above this #include

//-----------------------------------------------------------------------------

// Global Variables

//-----------------------------------------------------------------------------

volatile BOOL GotSUD;

BOOL Rwuen;

BOOL Selfpwr;

volatile BOOL Sleep; // Sleep mode enable flag

WORD pDeviceDscr; // Pointer to Device Descriptor; Descriptors may be moved

WORD pDeviceQualDscr;

WORD pHighSpeedConfigDscr;

WORD pFullSpeedConfigDscr;

WORD pConfigDscr;

WORD pOtherConfigDscr;

WORD pStringDscr;

//-----------------------------------------------------------------------------

// Prototypes

//-----------------------------------------------------------------------------

void SetupCommand(void);

void TD_Init(void);

void TD_Poll(void);

BOOL TD_Suspend(void);

BOOL TD_Resume(void);

BOOL DR_GetDescriptor(void);

BOOL DR_SetConfiguration(void);

BOOL DR_GetConfiguration(void);

BOOL DR_SetInterface(void);

BOOL DR_GetInterface(void);

BOOL DR_GetStatus(void);

BOOL DR_ClearFeature(void);

BOOL DR_SetFeature(void);

BOOL DR_VendorCmnd(void);

// this table is used by the epcs macro

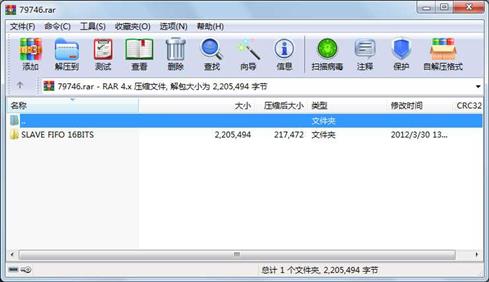

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 20990 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\db\altsyncram_lk81.tdf

文件 137 2012-10-29 14:43 SLAVE FIFO 16BITS\FPGA\db\USB_FPGA.db_info

文件 161 2012-10-29 14:43 SLAVE FIFO 16BITS\FPGA\db\USB_FPGA.eco.cdb

文件 154 2012-10-29 14:43 SLAVE FIFO 16BITS\FPGA\db\USB_FPGA.sld_design_entry.sci

文件 18972 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\prev_cmp_USB_FPGA.qmsg

文件 8722 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.asm.rpt

文件 303 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.cdf

文件 26 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.done

文件 72263 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.fit.eqn

文件 148460 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.fit.rpt

文件 411 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.fit.smsg

文件 424 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.fit.summary

文件 3764 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.flow.rpt

文件 64401 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.map.eqn

文件 39386 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.map.rpt

文件 332 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.map.summary

文件 30259 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.pin

文件 524492 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.pof

文件 902 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.qpf

文件 5775 2012-10-29 14:43 SLAVE FIFO 16BITS\FPGA\USB_FPGA.qsf

文件 534 2012-10-29 14:43 SLAVE FIFO 16BITS\FPGA\USB_FPGA.qws

文件 92674 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.sim.rpt

文件 140523 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.sof

文件 198554 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.tan.rpt

文件 1762 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.tan.summary

文件 4871 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.vhd

文件 4332 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.vhd.bak

文件 40975 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA.vwf

文件 27985 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\USB_FPGA_assignment_defaults.qdf

..A..H. 9 2012-03-30 13:24 SLAVE FIFO 16BITS\FPGA\_desktop.ini

............此处省略41个文件信息

- 上一篇:易语言读写excel超链接

- 下一篇:cvut库函数

相关资源

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- CY7C68013A固件程序(用于摄像机采集)

- CPLD Verilog数字密码锁 源码

- verilog 实现任意分频方法

- DE2模拟的交通红绿灯

- SPI Master 的Verilog源代码

- 基于VGA的Flappy Bird的Verilog实现(源码

- 数字钟

- Verilog的135个经典设计

- verilog 4×4矩阵键盘

- Quartus EDA交通灯控制电路的设计实训报

- FPGA按键消抖

- 用Verilog语言写的CPLD和MCU通讯的SPI接口

- ARM9指令cache的verilog代码

- ddr_verilog

- FPGA实现单极性SPWM调制

- uart_tx.zip

- 基于Verilog的cordic反正切FPGA例程

- SystemVerilog验证测试平台编写指南(中

- 基于Verilog的交通灯设计EDA课程设计

- 数字信号处理的FPGA实现Verilog源码

- verilog硬件描述语言程序设计与实践教

- Ultraedit环境下配置verilog语法高亮的字

- 8 位cpu的verilog

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论