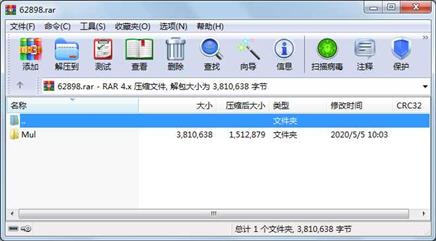

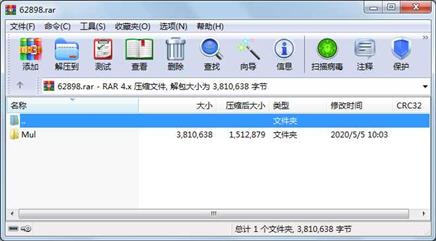

资源简介

Verilog原码二位乘法器,其中两个操作数位宽为5。文件中含解释文档,代码中含tb文件和详细注释。配合https://blog.csdn.net/qq_42334072/article/details/105928385食用更佳

代码片段和文件信息

/**********************************************************************/

/* ____ ____ */

/* / /\/ / */

/* /___/ \ / */

/* \ \ \/ */

/* \ \ Copyright (c) 2003-2013 Xilinx Inc. */

/* / / All Right Reserved. */

/* /---/ /\ */

/* \ \ / \ */

/* \___\/\___\ */

/**********************************************************************/

#include “iki.h“

#include

#include

#ifdef __GNUC__

#include

#else

#include

#define alloca _alloca

#endif

/**********************************************************************/

/* ____ ____ */

/* / /\/ / */

/* /___/ \ / */

/* \ \ \/ */

/* \ \ Copyright (c) 2003-2013 Xilinx Inc. */

/* / / All Right Reserved. */

/* /---/ /\ */

/* \ \ / \ */

/* \___\/\___\ */

/**********************************************************************/

#include “iki.h“

#include

#include

#ifdef __GNUC__

#include

#else

#include

#define alloca _alloca

#endif

typedef void (*funcp)(char * char *);

extern int main(int char**);

extern void execute_2(char* char *);

extern void execute_3(char* char *);

extern void execute_12(char* char *);

extern void execute_13(char* char *);

extern void execute_14(char* char *);

extern void execute_15(char* char *);

extern void execute_16(char* char *);

extern void execute_5(char* char *);

extern void execute_6(char* char *);

extern void execute_7(char* char *);

extern void execute_9(char* char *);

extern void execute_10(char* char *);

extern void execute_11(char* char *);

extern void execute_17(char* char *);

extern void execute_18(char* char *);

extern void execute_19(char* char *);

extern void execute_20(char* char *);

extern void execute_21(char* char *);

extern void vlog_transfunc_eventcallback(char* char* unsigned unsigned unsigned char *);

funcp funcTab[19] = {(funcp)execute_2 (funcp)execute_3 (funcp)execute_12 (funcp)execute_13 (funcp)execute_14 (funcp)execute_15 (funcp)execute_16 (funcp)execute_5 (f属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 5017 2020-05-05 11:01 Mul\Mul.cache\wt\gui_handlers.wdf

文件 1031 2020-05-05 11:01 Mul\Mul.cache\wt\java_command_handlers.wdf

文件 61 2020-05-05 10:03 Mul\Mul.cache\wt\project.wpc

文件 4944 2020-05-05 11:01 Mul\Mul.cache\wt\webtalk_pa.xm

文件 239 2020-05-05 10:21 Mul\Mul.cache\wt\xsim.wdf

文件 290 2020-05-03 16:34 Mul\Mul.hw\Mul.lpr

文件 130 2020-05-03 17:33 Mul\Mul.ip_user_files\README.txt

文件 830 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\compile.bat

文件 370 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\compile.log

文件 907 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\elaborate.bat

文件 725 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\elaborate.log

文件 1474 2018-12-07 12:04 Mul\Mul.sim\sim_1\behav\xsim\glbl.v

文件 458 2020-05-05 10:17 Mul\Mul.sim\sim_1\behav\xsim\Mul_tb.tcl

文件 15353 2020-05-05 11:01 Mul\Mul.sim\sim_1\behav\xsim\Mul_tb_behav.wdb

文件 269 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\Mul_tb_vlog.prj

文件 792 2020-05-05 10:17 Mul\Mul.sim\sim_1\behav\xsim\simulate.bat

文件 50 2020-05-05 11:01 Mul\Mul.sim\sim_1\behav\xsim\simulate.log

文件 881 2020-05-05 10:19 Mul\Mul.sim\sim_1\behav\xsim\webtalk.jou

文件 950 2020-05-05 10:19 Mul\Mul.sim\sim_1\behav\xsim\webtalk.log

文件 882 2020-05-03 17:34 Mul\Mul.sim\sim_1\behav\xsim\webtalk_12780.backup.jou

文件 951 2020-05-03 17:34 Mul\Mul.sim\sim_1\behav\xsim\webtalk_12780.backup.log

文件 881 2020-05-03 17:33 Mul\Mul.sim\sim_1\behav\xsim\webtalk_4140.backup.jou

文件 950 2020-05-03 17:33 Mul\Mul.sim\sim_1\behav\xsim\webtalk_4140.backup.log

文件 881 2020-05-05 10:17 Mul\Mul.sim\sim_1\behav\xsim\webtalk_8828.backup.jou

文件 950 2020-05-05 10:17 Mul\Mul.sim\sim_1\behav\xsim\webtalk_8828.backup.log

文件 1515 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\xelab.pb

文件 246 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\xsim.dir\Mul_tb_behav\Compile_Options.txt

文件 25984 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\xsim.dir\Mul_tb_behav\obj\xsim_0.win64.obj

文件 4873 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\xsim.dir\Mul_tb_behav\obj\xsim_1.c

文件 3123 2020-05-05 10:21 Mul\Mul.sim\sim_1\behav\xsim\xsim.dir\Mul_tb_behav\obj\xsim_1.win64.obj

............此处省略57个文件信息

- 上一篇:电磁场虚拟实验报告北理工

- 下一篇:TDOA定位系统

相关资源

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- CPLD Verilog数字密码锁 源码

- verilog 实现任意分频方法

- DE2模拟的交通红绿灯

- SPI Master 的Verilog源代码

- 基于VGA的Flappy Bird的Verilog实现(源码

- 数字钟

- Verilog的135个经典设计

- verilog 4×4矩阵键盘

- Quartus EDA交通灯控制电路的设计实训报

- FPGA按键消抖

- 用Verilog语言写的CPLD和MCU通讯的SPI接口

- ARM9指令cache的verilog代码

- ddr_verilog

- 基于FPGA的高速流水线浮点乘法器设计

- FPGA实现单极性SPWM调制

- uart_tx.zip

- 基于Verilog的cordic反正切FPGA例程

- SystemVerilog验证测试平台编写指南(中

- 基于Verilog的交通灯设计EDA课程设计

- 数字信号处理的FPGA实现Verilog源码

- verilog硬件描述语言程序设计与实践教

- Ultraedit环境下配置verilog语法高亮的字

- 8 位cpu的verilog

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论