资源简介

本程序完成以下功能

1. 基本部分

当控制开关启,固定间 隔一段时(例如 3s)之后,指示灯点亮。

完成一次测试后,将 被测试者的 反应时间显示在数码管上 。

如果指示灯点亮前, 被测试者按下键,视为违规应给出警示。

2. 2. 提高部分

(1)(1)(1)当控制开关启,随机间 隔一段时(时间不宜过长,例如 <= 5s)之后,指示灯点亮。

(2)(2) 两人比赛谁先按下键, 指示 谁是 获胜者 ,并显示其反应 时间。

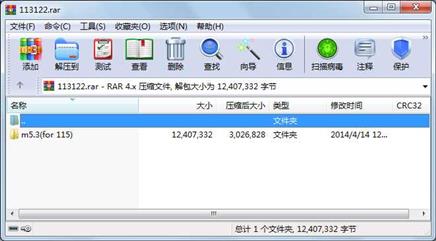

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 1262 2014-04-14 12:38 m5.3(for 115)\m51040.qpf

文件 4659 2014-06-20 15:16 m5.3(for 115)\m51040.qsf

文件 1289 2014-04-16 09:35 m5.3(for 115)\count_module.v.bak

文件 645 2014-04-16 09:41 m5.3(for 115)\who_first.v

文件 462 2014-06-20 15:16 m5.3(for 115)\m51040.map.summary

文件 639 2014-04-16 09:39 m5.3(for 115)\who_first.v.bak

文件 4422 2014-04-16 09:43 m5.3(for 115)\m51040.qsf.bak

文件 142 2014-04-15 00:35 m5.3(for 115)\m51040.map.smsg

文件 27419 2014-06-20 15:17 m5.3(for 115)\m51040.pin

文件 513 2014-06-20 15:17 m5.3(for 115)\m51040.fit.smsg

文件 601 2014-06-20 15:17 m5.3(for 115)\m51040.fit.summary

文件 151050 2014-06-20 15:17 m5.3(for 115)\m51040.sof

文件 524474 2014-06-20 15:17 m5.3(for 115)\m51040.pof

文件 1514 2014-06-20 15:17 m5.3(for 115)\m51040.tan.summary

文件 26 2014-06-20 15:17 m5.3(for 115)\m51040.done

文件 239 2014-04-15 09:27 m5.3(for 115)\m51040.dpf

文件 527 2014-04-15 23:20 m5.3(for 115)\key_win.v.bak

文件 1443 2014-04-15 23:35 m5.3(for 115)\time_count.v.bak

文件 1531 2014-04-15 23:42 m5.3(for 115)\constant_time_module.v.bak

文件 137 2014-04-14 12:38 m5.3(for 115)\db\m51040.db_info

文件 3392 2014-06-20 15:16 m5.3(for 115)\db\m51040.lpc.txt

文件 1771 2014-06-20 15:16 m5.3(for 115)\db\m51040.rtlv_sg_swap.cdb

文件 4248 2014-06-20 15:16 m5.3(for 115)\db\m51040.lpc.html

文件 254 2014-06-20 15:16 m5.3(for 115)\db\m51040.smp_dump.txt

文件 4 2014-06-20 15:16 m5.3(for 115)\db\m51040.map_bb.logdb

文件 1941 2014-06-14 19:14 m5.3(for 115)\db\lpm_divide_dem.tdf

文件 46675 2014-06-20 15:16 m5.3(for 115)\db\m51040.sgdiff.cdb

文件 424 2014-06-20 15:16 m5.3(for 115)\db\m51040.cbx.xml

文件 416956 2014-06-20 15:17 m5.3(for 115)\db\m51040.fit.qmsg

文件 2190 2014-06-20 15:17 m5.3(for 115)\db\m51040.asm.qmsg

............此处省略196个文件信息

----------- --------- ---------- ----- ----

文件 1262 2014-04-14 12:38 m5.3(for 115)\m51040.qpf

文件 4659 2014-06-20 15:16 m5.3(for 115)\m51040.qsf

文件 1289 2014-04-16 09:35 m5.3(for 115)\count_module.v.bak

文件 645 2014-04-16 09:41 m5.3(for 115)\who_first.v

文件 462 2014-06-20 15:16 m5.3(for 115)\m51040.map.summary

文件 639 2014-04-16 09:39 m5.3(for 115)\who_first.v.bak

文件 4422 2014-04-16 09:43 m5.3(for 115)\m51040.qsf.bak

文件 142 2014-04-15 00:35 m5.3(for 115)\m51040.map.smsg

文件 27419 2014-06-20 15:17 m5.3(for 115)\m51040.pin

文件 513 2014-06-20 15:17 m5.3(for 115)\m51040.fit.smsg

文件 601 2014-06-20 15:17 m5.3(for 115)\m51040.fit.summary

文件 151050 2014-06-20 15:17 m5.3(for 115)\m51040.sof

文件 524474 2014-06-20 15:17 m5.3(for 115)\m51040.pof

文件 1514 2014-06-20 15:17 m5.3(for 115)\m51040.tan.summary

文件 26 2014-06-20 15:17 m5.3(for 115)\m51040.done

文件 239 2014-04-15 09:27 m5.3(for 115)\m51040.dpf

文件 527 2014-04-15 23:20 m5.3(for 115)\key_win.v.bak

文件 1443 2014-04-15 23:35 m5.3(for 115)\time_count.v.bak

文件 1531 2014-04-15 23:42 m5.3(for 115)\constant_time_module.v.bak

文件 137 2014-04-14 12:38 m5.3(for 115)\db\m51040.db_info

文件 3392 2014-06-20 15:16 m5.3(for 115)\db\m51040.lpc.txt

文件 1771 2014-06-20 15:16 m5.3(for 115)\db\m51040.rtlv_sg_swap.cdb

文件 4248 2014-06-20 15:16 m5.3(for 115)\db\m51040.lpc.html

文件 254 2014-06-20 15:16 m5.3(for 115)\db\m51040.smp_dump.txt

文件 4 2014-06-20 15:16 m5.3(for 115)\db\m51040.map_bb.logdb

文件 1941 2014-06-14 19:14 m5.3(for 115)\db\lpm_divide_dem.tdf

文件 46675 2014-06-20 15:16 m5.3(for 115)\db\m51040.sgdiff.cdb

文件 424 2014-06-20 15:16 m5.3(for 115)\db\m51040.cbx.xm

文件 416956 2014-06-20 15:17 m5.3(for 115)\db\m51040.fit.qmsg

文件 2190 2014-06-20 15:17 m5.3(for 115)\db\m51040.asm.qmsg

............此处省略196个文件信息

相关资源

- EDA课程设计_密码锁

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- CPLD Verilog数字密码锁 源码

- verilog 实现任意分频方法

- DE2模拟的交通红绿灯

- EDA课程设计(出租车计费系统)

- SPI Master 的Verilog源代码

- 基于VGA的Flappy Bird的Verilog实现(源码

- 数字钟

- Verilog的135个经典设计

- verilog 4×4矩阵键盘

- Quartus EDA交通灯控制电路的设计实训报

- FPGA按键消抖

- 用Verilog语言写的CPLD和MCU通讯的SPI接口

- ARM9指令cache的verilog代码

- 基于Freemarker模板的代码生成器后台代

- ddr_verilog

- FPGA实现单极性SPWM调制

- uart_tx.zip

- 基于Verilog的cordic反正切FPGA例程

- 数字系统综合设计 eda 模拟中央人民广

- SystemVerilog验证测试平台编写指南(中

- 基于Verilog的交通灯设计EDA课程设计

- 数字信号处理的FPGA实现Verilog源码

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论