资源简介

产生的信号可以是正弦波或方波、三角波、锯齿波;可以用SignalTap逻辑分析。可以用Model Sim仿真。全部打包在文件中。工程适用版本为Quartus II 13.0,不可低于该版本。

原理:采用DDS技术,将所需生成的波形写入ROM中,按照相位累加原理合成任意波形。

此方案得到的波形稳定,精度高,产生波形频率范围大,容易产生高频。

本实验在设计的模块中,包含以下功能:

(1)通过 freq 信号输入需要的频率的值;

(2)通过 wave_sel 信号选择所需的波形;

(3)通过 amp_adj 信号选择波形放大的倍数。

在该设计中,包含 3 个模块:

频率控制器,根据输入的频率值输出步进值 step_val 。

相位累加器,根据步进值 step_val 控制对应地址的变化。

波形放大器,对 rom 输出的数据进行放大。

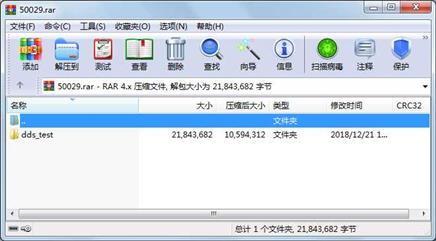

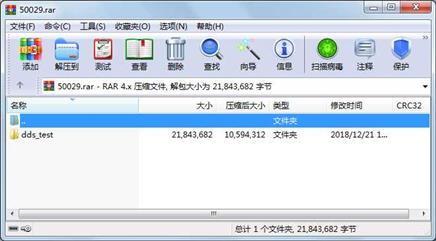

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 4875 2018-12-21 17:30 dds_test\c5_pin_model_dump.txt

文件 759 2018-12-21 17:30 dds_test\db\.cmp.kpt

文件 19137 2018-12-21 17:29 dds_test\db\altsyncram_e784.tdf

文件 40698 2018-12-21 16:51 dds_test\db\altsyncram_i784.tdf

文件 10430 2018-12-18 22:18 dds_test\db\altsyncram_maf1.tdf

文件 21201 2018-12-21 16:22 dds_test\db\altsyncram_q484.tdf

文件 9683 2018-12-21 13:20 dds_test\db\alt_u_div_qse.tdf

文件 1681 2018-12-21 16:22 dds_test\db\cmpr_99c.tdf

文件 1913 2018-12-21 16:22 dds_test\db\cmpr_c9c.tdf

文件 2003 2018-12-21 16:51 dds_test\db\cmpr_d9c.tdf

文件 4082 2018-12-21 16:22 dds_test\db\cntr_09i.tdf

文件 3671 2018-12-21 16:51 dds_test\db\cntr_19i.tdf

文件 4248 2018-12-21 16:51 dds_test\db\cntr_29i.tdf

文件 3994 2018-12-21 16:22 dds_test\db\cntr_4vi.tdf

文件 4836 2018-12-21 16:51 dds_test\db\cntr_82j.tdf

文件 3542 2018-12-21 16:22 dds_test\db\cntr_kri.tdf

文件 4082 2018-12-21 17:29 dds_test\db\cntr_t8i.tdf

文件 4082 2018-12-21 16:22 dds_test\db\cntr_v8i.tdf

文件 3021 2018-12-21 17:15 dds_test\db\dds.(0).cnf.cdb

文件 1477 2018-12-21 17:15 dds_test\db\dds.(0).cnf.hdb

文件 2532 2018-12-21 17:15 dds_test\db\dds.(1).cnf.cdb

文件 1264 2018-12-21 17:15 dds_test\db\dds.(1).cnf.hdb

文件 7418 2018-12-21 13:20 dds_test\db\dds.(10).cnf.cdb

文件 4292 2018-12-21 13:20 dds_test\db\dds.(10).cnf.hdb

文件 1303 2018-12-21 16:53 dds_test\db\dds.(100).cnf.cdb

文件 752 2018-12-21 16:53 dds_test\db\dds.(100).cnf.hdb

文件 4482 2018-12-21 17:09 dds_test\db\dds.(101).cnf.cdb

文件 1254 2018-12-21 17:09 dds_test\db\dds.(101).cnf.hdb

文件 1374 2018-12-21 17:09 dds_test\db\dds.(102).cnf.cdb

文件 752 2018-12-21 17:09 dds_test\db\dds.(102).cnf.hdb

............此处省略466个文件信息

----------- --------- ---------- ----- ----

文件 4875 2018-12-21 17:30 dds_test\c5_pin_model_dump.txt

文件 759 2018-12-21 17:30 dds_test\db\.cmp.kpt

文件 19137 2018-12-21 17:29 dds_test\db\altsyncram_e784.tdf

文件 40698 2018-12-21 16:51 dds_test\db\altsyncram_i784.tdf

文件 10430 2018-12-18 22:18 dds_test\db\altsyncram_maf1.tdf

文件 21201 2018-12-21 16:22 dds_test\db\altsyncram_q484.tdf

文件 9683 2018-12-21 13:20 dds_test\db\alt_u_div_qse.tdf

文件 1681 2018-12-21 16:22 dds_test\db\cmpr_99c.tdf

文件 1913 2018-12-21 16:22 dds_test\db\cmpr_c9c.tdf

文件 2003 2018-12-21 16:51 dds_test\db\cmpr_d9c.tdf

文件 4082 2018-12-21 16:22 dds_test\db\cntr_09i.tdf

文件 3671 2018-12-21 16:51 dds_test\db\cntr_19i.tdf

文件 4248 2018-12-21 16:51 dds_test\db\cntr_29i.tdf

文件 3994 2018-12-21 16:22 dds_test\db\cntr_4vi.tdf

文件 4836 2018-12-21 16:51 dds_test\db\cntr_82j.tdf

文件 3542 2018-12-21 16:22 dds_test\db\cntr_kri.tdf

文件 4082 2018-12-21 17:29 dds_test\db\cntr_t8i.tdf

文件 4082 2018-12-21 16:22 dds_test\db\cntr_v8i.tdf

文件 3021 2018-12-21 17:15 dds_test\db\dds.(0).cnf.cdb

文件 1477 2018-12-21 17:15 dds_test\db\dds.(0).cnf.hdb

文件 2532 2018-12-21 17:15 dds_test\db\dds.(1).cnf.cdb

文件 1264 2018-12-21 17:15 dds_test\db\dds.(1).cnf.hdb

文件 7418 2018-12-21 13:20 dds_test\db\dds.(10).cnf.cdb

文件 4292 2018-12-21 13:20 dds_test\db\dds.(10).cnf.hdb

文件 1303 2018-12-21 16:53 dds_test\db\dds.(100).cnf.cdb

文件 752 2018-12-21 16:53 dds_test\db\dds.(100).cnf.hdb

文件 4482 2018-12-21 17:09 dds_test\db\dds.(101).cnf.cdb

文件 1254 2018-12-21 17:09 dds_test\db\dds.(101).cnf.hdb

文件 1374 2018-12-21 17:09 dds_test\db\dds.(102).cnf.cdb

文件 752 2018-12-21 17:09 dds_test\db\dds.(102).cnf.hdb

............此处省略466个文件信息

- 上一篇:Bad.Data.Handbook

- 下一篇:妹子图爬虫批量妹子图.rar

相关资源

- 一个labview仿真的函数信号发生器.vi

- Quartus II 15.0中仿真Altera三速以太网I

- Quartus II 15.0中仿真Altera三速以太网I

- 数字频率合成dds正弦波基于FPGA的DDS产

- 3人表决器 QuartusII

- 硬件课程设计—流水灯(quartus软件

- 曼彻斯特编解码_同步QuartusII工程

- CPLD Verilog数字密码锁 源码

- 用quartus 2编的全加器(原理图输入)

- 6相12拍步进电机控制器

- Quartus EDA交通灯控制电路的设计实训报

- Quartus II 15.0中仿真DDR2 IP核

- DAT DDS 磁带机DAT 72产品手册

- 可编程正弦波信号发生器电路图

- 正弦波信号发生器电路

- 基于protues的信号发生器,protues详细教

- quartus 11.0 破解包 全

- Quartusii十字交叉路口三色交通灯设计

- fpga DDS 信号发生器_v2

- 中值滤波算法Quartus实现

- VHDL简易交通灯设计 quartus 2

- quartus14.1破解包

- 基于quartus II的VHDL数字钟设计

- tgaddsmax缩略图显示插件大全.7z

- 基于FPGA的双通道幅度相位频率可调节

- quartus 16.1破解教程

- 基于Quartus II 9.0版本编写的Verilog HDL编

- QuartusII15.0安装包安装步骤.pdf

- 基于stm32和ad9850的dds信号源

- MSP430信号发生器.rar

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论