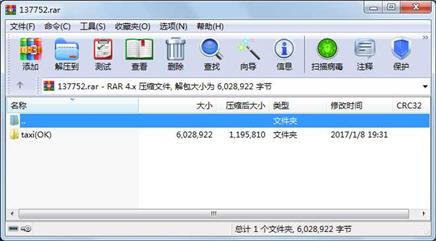

资源简介

本设计是使用Verilog实现出租车计费器,使用的开发平台是QuartusII开发软件,使用的开发板是DE2开发板

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 65 2016-12-24 21:15 taxi(OK)\.sopc_builder\filters.xml

文件 402 2016-12-24 21:15 taxi(OK)\.sopc_builder\preferences.xml

文件 1116 2016-12-25 09:38 taxi(OK)\BCD.v

文件 1095 2016-12-24 20:11 taxi(OK)\BCD.v.bak

文件 2905 2016-12-26 10:33 taxi(OK)\count_km.v

文件 2898 2016-12-26 10:31 taxi(OK)\count_km.v.bak

文件 478 2016-12-26 10:41 taxi(OK)\count_money.v

文件 472 2016-12-26 10:38 taxi(OK)\count_money.v.bak

文件 1428 2016-12-22 19:42 taxi(OK)\db\add_sub_k8h.tdf

文件 1428 2016-12-22 19:42 taxi(OK)\db\add_sub_l8h.tdf

文件 1730 2016-12-25 20:17 taxi(OK)\db\add_sub_lkc.tdf

文件 1875 2016-12-25 20:17 taxi(OK)\db\add_sub_mkc.tdf

文件 30787 2016-12-25 20:18 taxi(OK)\db\alt_u_div_g2f.tdf

文件 50521 2016-12-26 09:20 taxi(OK)\db\alt_u_div_i2f.tdf

文件 36599 2016-12-25 20:17 taxi(OK)\db\alt_u_div_o2f.tdf

文件 1941 2016-12-25 20:18 taxi(OK)\db\lpm_divide_dem.tdf

文件 1941 2016-12-26 09:20 taxi(OK)\db\lpm_divide_eem.tdf

文件 1941 2016-12-25 20:17 taxi(OK)\db\lpm_divide_hem.tdf

文件 2572 2016-12-26 08:53 taxi(OK)\db\mult_0v01.tdf

文件 2570 2016-12-26 08:42 taxi(OK)\db\mult_jt01.tdf

文件 2570 2016-12-22 16:20 taxi(OK)\db\mult_pt01.tdf

文件 2570 2016-12-25 20:17 taxi(OK)\db\mult_qt01.tdf

文件 2182 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.asm.qmsg

文件 79320 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.fit.qmsg

文件 29834 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.map.qmsg

文件 189956 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.qmsg

文件 78388 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.tan.qmsg

文件 2060 2016-12-25 20:18 taxi(OK)\db\sign_div_unsign_nlh.tdf

文件 2060 2016-12-26 09:20 taxi(OK)\db\sign_div_unsign_olh.tdf

文件 2060 2016-12-25 20:17 taxi(OK)\db\sign_div_unsign_rlh.tdf

............此处省略162个文件信息

----------- --------- ---------- ----- ----

文件 65 2016-12-24 21:15 taxi(OK)\.sopc_builder\filters.xm

文件 402 2016-12-24 21:15 taxi(OK)\.sopc_builder\preferences.xm

文件 1116 2016-12-25 09:38 taxi(OK)\BCD.v

文件 1095 2016-12-24 20:11 taxi(OK)\BCD.v.bak

文件 2905 2016-12-26 10:33 taxi(OK)\count_km.v

文件 2898 2016-12-26 10:31 taxi(OK)\count_km.v.bak

文件 478 2016-12-26 10:41 taxi(OK)\count_money.v

文件 472 2016-12-26 10:38 taxi(OK)\count_money.v.bak

文件 1428 2016-12-22 19:42 taxi(OK)\db\add_sub_k8h.tdf

文件 1428 2016-12-22 19:42 taxi(OK)\db\add_sub_l8h.tdf

文件 1730 2016-12-25 20:17 taxi(OK)\db\add_sub_lkc.tdf

文件 1875 2016-12-25 20:17 taxi(OK)\db\add_sub_mkc.tdf

文件 30787 2016-12-25 20:18 taxi(OK)\db\alt_u_div_g2f.tdf

文件 50521 2016-12-26 09:20 taxi(OK)\db\alt_u_div_i2f.tdf

文件 36599 2016-12-25 20:17 taxi(OK)\db\alt_u_div_o2f.tdf

文件 1941 2016-12-25 20:18 taxi(OK)\db\lpm_divide_dem.tdf

文件 1941 2016-12-26 09:20 taxi(OK)\db\lpm_divide_eem.tdf

文件 1941 2016-12-25 20:17 taxi(OK)\db\lpm_divide_hem.tdf

文件 2572 2016-12-26 08:53 taxi(OK)\db\mult_0v01.tdf

文件 2570 2016-12-26 08:42 taxi(OK)\db\mult_jt01.tdf

文件 2570 2016-12-22 16:20 taxi(OK)\db\mult_pt01.tdf

文件 2570 2016-12-25 20:17 taxi(OK)\db\mult_qt01.tdf

文件 2182 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.asm.qmsg

文件 79320 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.fit.qmsg

文件 29834 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.map.qmsg

文件 189956 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.qmsg

文件 78388 2016-12-26 10:33 taxi(OK)\db\prev_cmp_taxi.tan.qmsg

文件 2060 2016-12-25 20:18 taxi(OK)\db\sign_div_unsign_nlh.tdf

文件 2060 2016-12-26 09:20 taxi(OK)\db\sign_div_unsign_olh.tdf

文件 2060 2016-12-25 20:17 taxi(OK)\db\sign_div_unsign_rlh.tdf

............此处省略162个文件信息

- 上一篇:安装程序缺失ICA.msi,可这个

- 下一篇:以太网测试方法和指标

相关资源

- FPGA实现PID.v

- 基于FPGA的sdi视频传输工程(k7_sdi_rx

- FPGA彩条显示

- Xilinx-FPGA-引脚功能详细介绍.doc

- 基于xilinx FPGA的PCIe设计实战

- 基于PCIe的FPGA动态配置设计与实现

- 为什么工程师要掌握FPGA开发知识?

- 数字频率合成dds正弦波基于FPGA的DDS产

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- FPGA在步进电机驱动上的应用实例及代

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- fpga实现频率测量

- FPGA开发-ChipScope教程

- 红外循迹小车VHDL程序

- CPLD Verilog数字密码锁 源码

- 出租车计费器系统的设计

- verilog 实现任意分频方法

- 基于FPGA的USB接口设计

- DE2模拟的交通红绿灯

- SPI Master 的Verilog源代码

- 一种抗SEU存储器电路的FPGA设计

- Cyclone 10LP Remote Update Intel FPGA IP 官方工

- nRF24L01无线模块在单片机与FPGA上的应

- 基于FPGA多协议转换网关设计

- 基于VGA的Flappy Bird的Verilog实现(源码

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论