资源简介

使用Verilog实现16位单周期CPU,并且进行PCPU的软件仿真

之前上传的那个是32位的,传错了不好意思

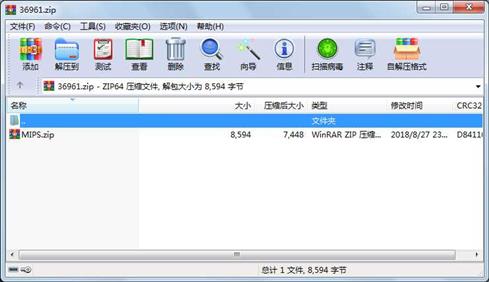

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 8594 2018-08-27 23:10 MIPS.zip

----------- --------- ---------- ----- ----

文件 8594 2018-08-27 23:10 MIPS.zip

- 上一篇:利用联合对角化技术进行信号盲分离

- 下一篇:汇编语言实现数字的输入排序显示

相关资源

- 基于MIPS指令集的32位CPU设计与Verilog语

- 用8位spi实现16位spi

- 看MIPS跑Linux第二版.pdf

- 16位MSP430单片机的开关稳压电源设计

- mips32系统架构手册

- 16位补码并行加法器含减法器实验

- MIPS多周期流水线CPU设计

- 五级流水线MIPS指令集cpu设计,verilo

- FPGA实现简单MIPS指令

- 计算机组成原理16位改8位CPU

- 基于verilog的MIPS32单周期CPU设计与实现

- MIPSsimMIPS指令系统模拟器.zip

- openwrt-18.06.4-ramips-mt7621-hc5962-squashfs-

- 0508-openwrt-ramips-rt305x-hg255d-squashfs-By_

- 多周期五段流水线MIPS CPU

- dynamipsGUIv2.8cn.rar

- 32位MIPS微处理器

- mips多周期五段流水线

- 16位实验CPU设计介绍

- 12条MIPS指令多周期CPU设计

- 数字逻辑与处理器实验——MIPS处理器

- 2.83版小凡模拟器 DynamipsGUI 中文最新版

- 基于MIPS指令集的32位CPU设计与Verilog语

- 基于stm32采集16位的ads1118

- VHDL 16位CPU

- 基于MIPS指令集的32位CPU设计与Verilog语

- VHDL基于MIPS指令集的32位CPU设计含源码

- 英飞凌16位单片机XC2000中文手册

- 李玮超基于MIPS指令集的32位CPU设计与

- MIPS32指令集.pdf

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论